Board 50227: verschil tussen versies

(→display mapping) |

(→LEDS) |

||

| Regel 78: | Regel 78: | ||

= LEDS = | = LEDS = | ||

| + | An identical circuit with a 74hc138 and 74hc174 seems to have been applied, as on [[Board 50229|50229]], connected to the same I/O lines. Because there are more LED's, port A5 is also used for an extra bit. | ||

| − | + | PORTA 0 downto 5 is used to load LED data into the 74HC174 flipflops, a 74HC183 is used to select which of the flipflops is put through to the leds. On 50227 there are 21 LED's. The unused last 3 inputs of the 4th flipflop are held high. | |

| + | |||

| + | To enable the demux that is driving the flipflop clock: | ||

| + | * nE1 connects to PC6 - drive LOW to enable LED's | ||

| + | * nE2 connects to PC7 - drive LOW to enable LED's | ||

| + | * E3 connects to PC5 - drive HIGH to enable LED's | ||

| + | |||

| + | The adress lines are as folows (This selects which one of the flipflops/registers is put trough to the leds) | ||

| + | * A0 connects to PC3 | ||

| + | * A1 connects to PC4 | ||

| + | * A2 connects to PD6 | ||

| + | |||

| + | The flipflop datalines: | ||

| + | * D0 connects to PA0 | ||

| + | * D1 connects to PA1 | ||

| + | * D2 connects to PA2 | ||

| + | * D3 connects to PA3 | ||

| + | * D4 connects to PA4 | ||

| + | * D5 connects to PA5 | ||

| + | |||

| + | So this is how to drive the LED's: | ||

| + | |||

| + | * Drive all adress lines (PC3,4 & PD6) low, so none of the clock inputs is driven. | ||

| + | * Put data on PA0..5 as per below table | ||

| + | * Choose 74hc174 as per below table | ||

| + | * Set adress lines such that the 174 gets a rising clock edge so it clocks the data to the LED's | ||

| + | * repeat | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | | '''PA0''' || 18R || 36R || 04 || CORR | ||

| + | |- | ||

| + | | '''PA1''' || 18C || 27 || 3 || 3' | ||

| + | |- | ||

| + | | '''PA2''' || 09 || 2 || 2' || EXEC | ||

| + | |- | ||

| + | | '''PA3''' || HELI || 1 || 36C || unused | ||

| + | |- | ||

| + | | '''PA4''' || 1' || 18C || 06 || unused | ||

| + | |- | ||

| + | | '''PA5''' || 36L || 24 || 22 || unused | ||

| + | |- | ||

| + | | 74HC174 nummer : || 0 || 1 || 2 || 3 | ||

| + | |} | ||

Versie van 1 jul 2021 om 22:34

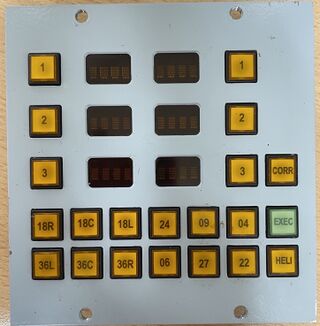

Seems similar to the 50229 board, but other display type (DLO1414 vs PD4435), other MCU (atmega161 where 50229 has a '162), and more buttons.

Seems like we have just 1 of this board. It might be similar to Bestand:IMG_8958.jpeg which then would be a second one.

buttons

4 extra buttons; wired between row 0/1, row 1/2 and col 1/2, col 2/3.

display mapping

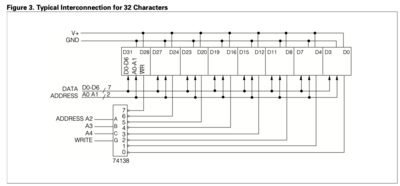

6 displays (DLO1414) - mapped per below; with from left to right in each screen '3210'.

Displays zitten aangesloten volgens het voorbeeld uit de datasheet, op de 74HC138 rechtsboven de atmega161.

Echter, er worden meer enable-pinnen gebruikt dan in het voorbeeld schema. Zie onderstaande tabel. Tussen haakjes de namen uit de 74HC138 datasheet achter de namen uit het voorbeeldschema.

| Atmega161 | 74hc138 |

|---|---|

| pin 24 PC3 | A (A0) |

| pin 25 PC4 | B (A1) |

| pin 26 PC5 | C (A2) |

| pin 27 PC6 | G (E3) |

| pin 28 PC7 | (nE1) |

| pin 16 PD6 nWR | (nE2) |

De datalijnen D0-D6 zitten op PA0-PA6 van de atmega161 (pin 39 PA0 tot pin 33 PA6). Er is bij dit type display geen D7.

reading the buttons

The 21 buttons are mostly in a 4x4 matrix. Every switch is between two MCU pins. The pins not fitting in the matrix are between 2 rows or 2 collumns.

The buttons 1, 2, 3 on the left are named 1, 2, 3 in the tables as well. The buttons labeled 1, 2, 3 on the right are labeled 1' 2' 3' as these are not in parallel with the others labeled 1, 2, 3.

| row/col | PD2 | PD3 | PD4 | PD5 |

| PB3 | 36C | 2' | 3 | 04 |

| PB2 | 24 | 18C | 1 | 2 |

| PB1 | 27 | 36R | 36L | 1' |

| PB0 | HELI | 09 | 18L | 18R |

The keys that are between 2 row lines or between 2 collumn lines can be re-fitted in another matrix: (Possibly other configurations are possible and maybe even more efficient! By choosing other row/col lines in software for the same hardware)

| row/col | PD5 | PB2 | PD3 | PB0 |

| PD4 | 3' | . | EXEC | . |

| PB3 | . | CORR | . | . |

| PB1 | . | 22 | . | 06 |

The keys are thus NOT the same als on 50229.

Read as any other keyboard matrix (? Enable pull-ups on input row/col s & unused col/row and drive one col/row low ?)

LEDS

An identical circuit with a 74hc138 and 74hc174 seems to have been applied, as on 50229, connected to the same I/O lines. Because there are more LED's, port A5 is also used for an extra bit.

PORTA 0 downto 5 is used to load LED data into the 74HC174 flipflops, a 74HC183 is used to select which of the flipflops is put through to the leds. On 50227 there are 21 LED's. The unused last 3 inputs of the 4th flipflop are held high.

To enable the demux that is driving the flipflop clock:

- nE1 connects to PC6 - drive LOW to enable LED's

- nE2 connects to PC7 - drive LOW to enable LED's

- E3 connects to PC5 - drive HIGH to enable LED's

The adress lines are as folows (This selects which one of the flipflops/registers is put trough to the leds)

- A0 connects to PC3

- A1 connects to PC4

- A2 connects to PD6

The flipflop datalines:

- D0 connects to PA0

- D1 connects to PA1

- D2 connects to PA2

- D3 connects to PA3

- D4 connects to PA4

- D5 connects to PA5

So this is how to drive the LED's:

- Drive all adress lines (PC3,4 & PD6) low, so none of the clock inputs is driven.

- Put data on PA0..5 as per below table

- Choose 74hc174 as per below table

- Set adress lines such that the 174 gets a rising clock edge so it clocks the data to the LED's

- repeat

| PA0 | 18R | 36R | 04 | CORR |

| PA1 | 18C | 27 | 3 | 3' |

| PA2 | 09 | 2 | 2' | EXEC |

| PA3 | HELI | 1 | 36C | unused |

| PA4 | 1' | 18C | 06 | unused |

| PA5 | 36L | 24 | 22 | unused |

| 74HC174 nummer : | 0 | 1 | 2 | 3 |